SAMIT BASU OSDA 24 VIRTUAL

# RUST AS A HARDWARE DESCRIPTION LANGUAGE

# WHY RUST?

Safety - stop errors at compile at edit time!

- Reuse & Sharing package manager, generics, and crates

- Testing built-in, batteries included

- **Tooling** IDE support

## RustHDL

- Open Source

- Transpile AST

- Event-based simulator

- Medium scale designs

- developed

- tested

- commercially deployed

https://rust-hdl.org/

(Source, Docs, Discord)

### RustHDL Tutorial

Alchitry Cu - Blinky Tutorial - 5min 🖄

Safe

Use rustc to check the validity of your firmware with strongly typed interfaces that are checked at *compile* time.

Easily package complex designs into easy-to-reuse modules that you can reuse easily. Connecting components is simple and missing or erroneous connections are caught at compile time or with the built in static analysis passes

### GitHub 🖸 🔅 API Docs 🖸 Crates 📦 🗹

Write FPGA Firmware using Rust! 🤌 👾

### Powerful

### **Batteries Included**

Need an asynchronous FIFO? Or a SDR memory controller? Or a one shot? Use the provided set of widgets to get started. Most are generic and can be used to handle arbitrary data types.

# **COMPARISON TO OTHER HDLS**

|                    | RustHDL               | CHISEL                   | MyHDL             |

|--------------------|-----------------------|--------------------------|-------------------|

| Embedding Language | Rust                  | SCALA                    | Python            |

| Types              | Strong and static     | Strong and static        | Loose and dynamic |

| Coding style       | Behavioral imperative | Structural<br>Generators | Generators        |

| Ecosystem          | <u>crates.io</u>      | MavenCentral             | pypi              |

| Metaprogramming    | Generics and Macros   | Generics                 | Yes               |

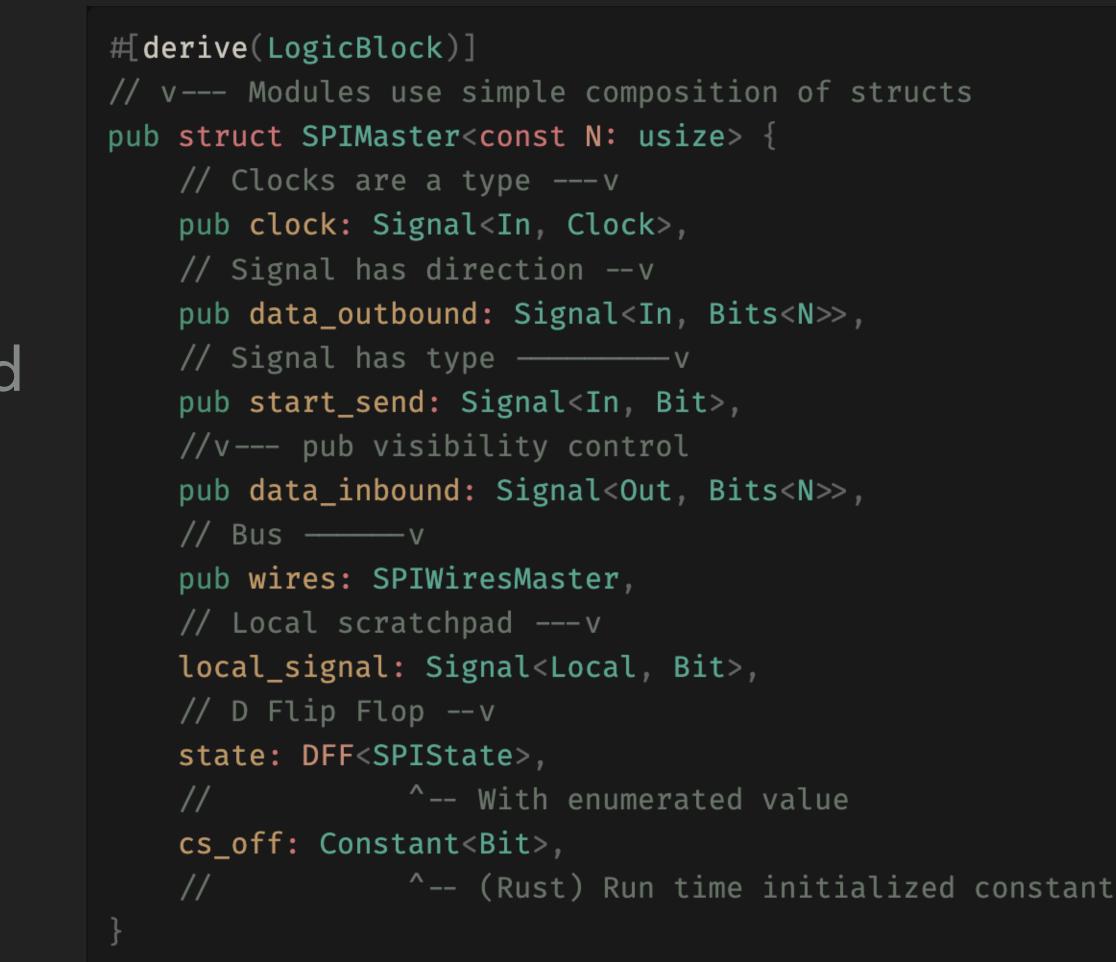

# STRUCTURE

- Circuits are composed into structs

- Input/output signals (ports) also composed

- pub controls visibility

- Encapsulation and reuse

- Designs are hierarchical

# CONNECT

- State encapsulated in D Flip Flops, BRAMs, etc.

- Code is **valid** Rust

- Latch prevention via yosys

- Rust-like (sane) scoping

```

// Design is parametric over N - the size of the counter

impl<const N: usize> Logic for Strobe<N> {

// v-- Attribute to generate HDL

#[hdl_gen]

// v-- Update function is attached to any logic circuit

fn update(&mut self) {

// v-- latch prevention

self.counter.d.next = self.counter.q.val();

// v-- mux control signal

if self.enable.val() {

// v-- value assigned if mux control is true

self.counter.d.next = self.counter.q.val() + 1;

// v-- combinatorial logic

self.strobe.next = self.enable.val() &

(self.counter.q.val() = self.threshold.val());

// v-- higher priority mux for previous mux output

if self.strobe.val() {

self.counter.d.next = 1.into();

```

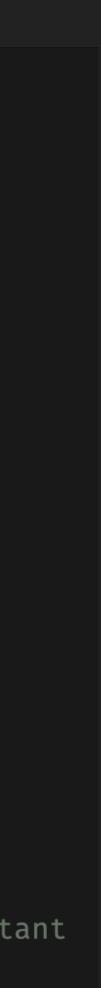

## **TOWARDS PURE FUNCTIONS**

- Idea taken from Lucid HDL

- Connect function maps current values to "next ones"

- Last update wins

- No surprises from blocking vs unblocking assignments...

```

// Design is parametric over N - the size of the counter

impl<const N: usize> Logic for Strobe<N> {

// v-- Attribute to generate HDL

#[hdl_gen]

// v-- Update function is attached to any logic circuit

fn update(&mut self) {

// v-- latch prevention

self.counter.d.next = self.counter.q.val();

// v-- mux control signal

if self.enable.val() {

// v-- value assigned if mux control is true

self.counter.d.next = self.counter.q.val() + 1;

// v-- combinatorial logic

self.strobe.next = self.enable.val() &

(self.counter.q.val() = self.threshold.val());

// v-- higher priority mux for previous mux output

if self.strobe.val() {

self.counter.d.next = 1.into();

```

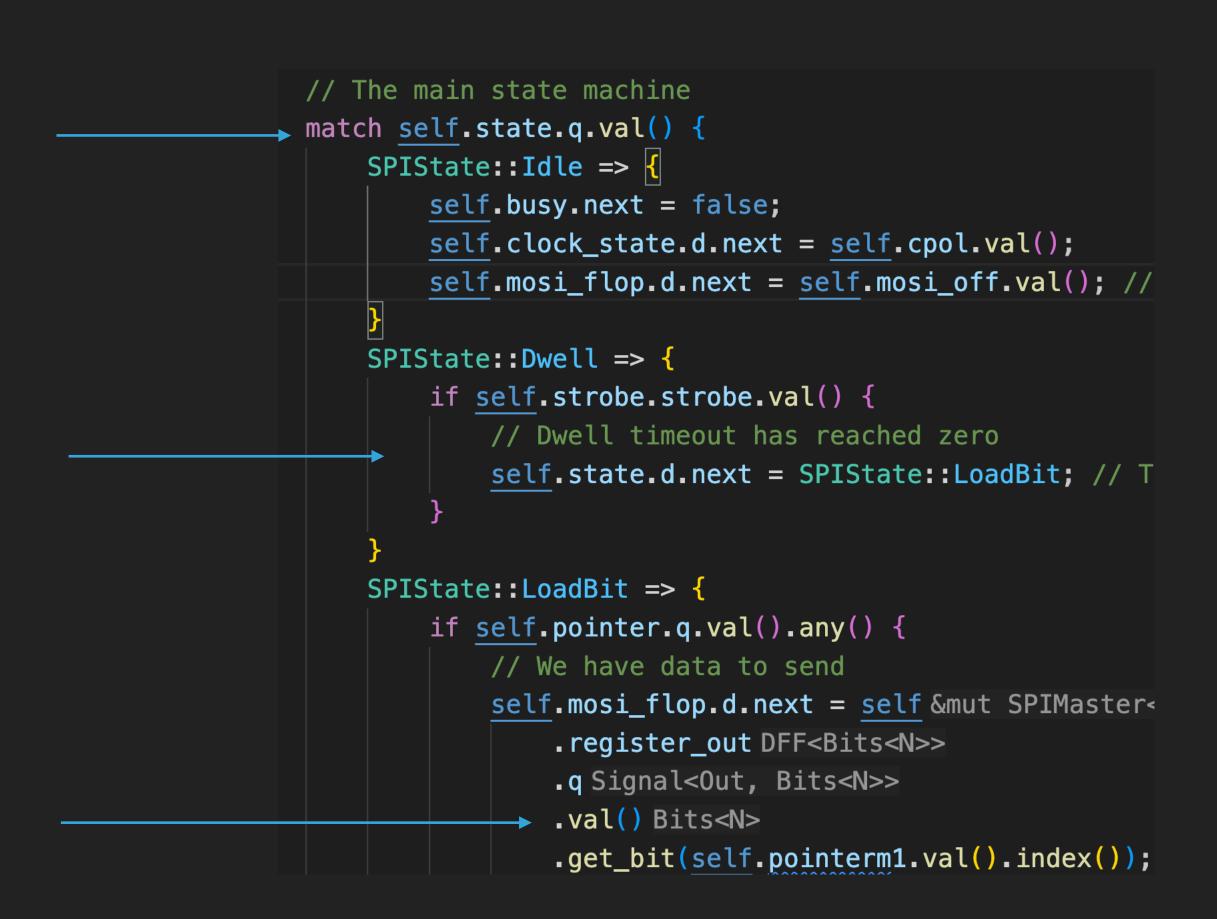

### FINITE STATE MACHINES

- Match on current state

- Rust match is exhaustive

- Next state is assigned here

- Improves readability

- Enums are simple and typed

- Note type hints from RA

### **SIMPLE ENUMS**

- Unlike C enums, these are strongly typed

- Rust guarantees that enum values are always valid

- Cannot carry data, just aliases for values

- Values are unspecified to allow for encoding optimization

### С #[derive(Copy, Clone, PartialEq, Debug, LogicState)] 4 7 implementations enum SPIState { 5 Idle, 6 7 Dwell, LoadBit, 8 MActive, 9 10 SampleMISO, 11 MIdle, 12 Finish, 13

# CONFIGURATION

- Circuits are configured at RustHDL run time

- Allows for arbitrary complexity in configuration

- Avoids need for external programs to compute tables/functions/etc.

- Add unit tests and functional tests to the configuration

```

pub fn snore<const P: usize>(x: u32) -> Bits<P> {

16

let amp: f64 = (f64::exp(self: f64::sin(self: ((x as f64) - 128))

17

let amp: u8 = (amp.max(0.0).min(255.0).floor() / 255.0 * (1 <<</pre>

18

amp.to_bits()

19

20

#[derive(LogicBlock)]

3 implementations

pub struct FaderWithSyncROM {

23

pub clock: Signal<In, Clock>,

24

pub active: Signal<Out, Bit>,

25

pub enable: Signal<In, Bit>,

26

strobe: Strobe<32>,

27

pwm: PulseWidthModulator<6>,

28

rom: SyncROM<Bits<6>, 8>,

29

30

counter: DFF<Bits<8>>,

31 }

32

impl FaderWithSyncROM {

33

pub fn new(clock_frequency: u64, phase: u32) -> Self {

34

let rom: BTreeMap<Bits<8>, Bits<6>> = (0..256) Range<u32>

35

.map(|x: u32| (x.to_bits(), snore(x + phase))) impl Iterator<Item = (Bits<8>, ...)>

36

37

.collect::<BTreeMap<_, _>>();

```

### **INTERFACES**

- Logical grouping of signals

- Can be nested

- Allow signals in both directions

Can join interfaces with a single line of code

```

v-- indicates its an interface

11

#[derive(LogicInterface, Clone, Debug, Default)]

v-- "mating" interface

//

#[join = "SDRAMDriver"]

pub struct SDRAMDevice<const D: usize> {

// Interfaces can be generic --^

pub clk: Signal<In, Clock>,

pub we_not: Signal<In, Bit>,

pub read_data: Signal<Out, Bits<D>>,

pub write_enable: Signal<In, Bit>,

```

```

fn update(&mut self) {

I2CBusDriver::join(&mut self.controller.i2c,

Smut self.test_bus.endpoints[0]);

```

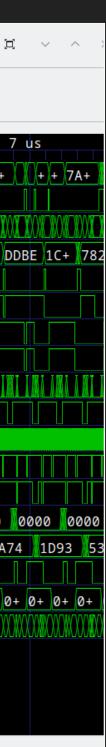

### SIMULATE FROM YOUR IDE 41 42 **#**[test] 44 45 46 No special configuration or 47 48 49 tooling 50 51 52 53 54 Batteries included 55 }); 56 57 58 59 Full debugging available 60 61 62 63 64 Set breakpoints based on state/ 65 66 }); 67 etc. 68 69 70

successes:

successes:

test result: ok. 1 passed; 0 failed; 0 ignored; 0 measured; 1 filtered out; finished in 1.24s

\* Terminal will be reused by tasks, press any key to close it.

Image: Book of the second second

tests > 🐵 core\_hls\_sdram\_fifo.rs > 🛇 test\_hls\_sdram\_fifo\_works

```

▶ Run Test | Debug

43 fn test_hls_sdram_fifo_works() {

let mut uut: HLSSDRAMFIF0Test = HLSSDRAMFIF0Test::default();

uut.fifo.bus_write.link_connect_dest();

uut.fifo.bus_read.link_connect_dest();

uut.connect_all();

let mut sim: Simulation<HLSSDRAMFIF0Test> = Simulation::new();

let data: Vec<u16> = (0..256) Range<i32>

.map(|_| rand::thread_rng().gen::<u16>()) impl Iterator<Item = u16>

.collect::<Vec<_>>();

let data2: Vec<u16> = data.clone();

sim.add_clock(interval: 4000, clock_fn: |x: &mut Box<HLSSDRAMFIF0Test>| {

<u>x</u>.clock.next = !<u>x</u>.clock.val()

sim.add_testbench(move |mut sim: Sim<HLSSDRAMFIF0Test>| {

let mut x: Box<HLSSDRAMFIF0Test> = sim.init()?;

wait_clock_cycles!(sim, clock, x, 20);

hls_fifo_write_lazy!(sim, clock, x, fifo.bus_write, &data);

sim.done(x)

});

sim.add_testbench(move |mut sim: Sim<HLSSDRAMFIF0Test>| {

let mut x: Box<HLSSDRAMFIF0Test> = sim.init()?;

wait_clock_cycles!(sim, clock, x, 20);

hls_fifo_read_lazy!(sim, clock, x, fifo.bus_read, &data2);

sim.done(x)

sim.run_to_file(x: Box::new(uut), max_time: 200_000_000, name: &vcd_path!("hls_sdram_fifo.vcd")) Result<(), SimEr</pre>

unwrap();

fn test_hls_sdram_fifo_works

```

PROBLEMS OUTPUT DEBUG CONSOLE TERMINAL PORTS

```

test_hls_sdram_fifo_works

```

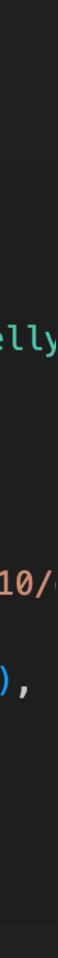

### BATTERIES INCLUDED

### SIMULATION

| <b>.</b> . | -                                                |        |      |       |     |                    |             |          |            |  |  |  |  |

|------------|--------------------------------------------------|--------|------|-------|-----|--------------------|-------------|----------|------------|--|--|--|--|

| = .        | X 🗅 🖻 🔅                                          |        | 5 16 | < >>  | < > | From:              | 0 sec       | To:      | 24084 ns   |  |  |  |  |

| ~sst       |                                                  |        |      |       |     | Signal             | S           |          |            |  |  |  |  |

|            | an_read                                          |        |      |       |     | Time               |             |          |            |  |  |  |  |

|            | an_write                                         |        |      |       |     |                    | data[15:0   | 0] =3068 |            |  |  |  |  |

|            | >  \$->  \$->  \$->  \$->  \$->  \$->  \$->  \$- |        |      |       |     |                    | rea         | ad =0    |            |  |  |  |  |

|            | dram_is_e                                        |        |      |       |     |                    | CI          | nd =NOP  |            |  |  |  |  |

|            |                                                  |        |      |       |     |                    | data[15:0   | 0] =2B23 |            |  |  |  |  |

|            | ់ ំdram_is_f                                     | uli    |      |       |     |                    | writ        | te=0     |            |  |  |  |  |

|            | - åfill                                          |        |      |       |     |                    | ful         | ll=1     |            |  |  |  |  |

|            | >fp                                              |        |      |       |     |                    | empt        | ty =0    |            |  |  |  |  |

|            | hread_poin                                       | ter    |      |       |     | almost_empty=0     |             |          |            |  |  |  |  |

|            | sdram                                            |        |      |       |     | address[12:0]=0000 |             |          |            |  |  |  |  |

|            | - state                                          |        |      |       |     |                    | cas_not=1   |          |            |  |  |  |  |

|            |                                                  | nter   |      |       |     |                    | c]          | lk=1     |            |  |  |  |  |

|            | sdram                                            |        |      |       |     |                    | ras_no      | ot=1     |            |  |  |  |  |

| ×          | sdram                                            |        |      |       |     |                    | we_no       | ot=1     |            |  |  |  |  |

| Tupo       | Signals                                          |        |      |       |     | read               | d_data[15:0 | 0] =0000 |            |  |  |  |  |

|            | Signals                                          |        |      |       |     | write              | e_data[15:0 | 0] =3283 |            |  |  |  |  |

|            | clock                                            |        |      |       |     | ١                  | write_enab] | le=0     |            |  |  |  |  |

| real       | d                                                |        |      |       |     |                    | q[11:0      | 0] =000  |            |  |  |  |  |

| real       |                                                  |        |      |       |     |                    |             | q=Auto   | refreshing |  |  |  |  |

|            |                                                  |        |      |       |     |                    |             |          |            |  |  |  |  |

| ٩          |                                                  |        |      |       |     |                    |             |          |            |  |  |  |  |

| A          | opend                                            | Insert |      | Repla | ce  |                    |             |          |            |  |  |  |  |

- Multiple clock domains

- Supports combinatorial inter-module logic and non-synchronous designs

- Example of SDRAM chip, controller, and a FIFO

| GTKWave/hls_    | sdram_fifo.vcd |

|-----------------|----------------|

| Marker: 4830 ns | Cursor: 0 sec  |

0

| Waves                           |            |          |          |         |       |         |            |           |                   |      |         |      |         |        |      |           |      |      |     |      |       |            |       |

|---------------------------------|------------|----------|----------|---------|-------|---------|------------|-----------|-------------------|------|---------|------|---------|--------|------|-----------|------|------|-----|------|-------|------------|-------|

| 0 1 us                          |            | 2 u      | IS       |         |       | 3 u     | IS         |           |                   | 4 u  | IS      |      |         | 5      | us   |           |      |      |     | 6 u  | S     |            |       |

| 0000                            |            |          | + 00     | 0+ 6    | D39   | XXX + + | + 3D02     | 2 0+ +    | 0+                | 00   | +       | 0+ + | 19+     | 3+     | 9B+  | XX        | 3+   | 2+   | +++ | 39   | 9+\+\ | 3F+        | 76+   |

|                                 |            |          |          |         |       |         |            |           |                   |      |         |      |         |        |      |           |      |      |     |      |       |            |       |

| OP                              | XX+X XX+X+ |          |          |         |       |         | X////X+    | X+XXX     |                   |      | XXX XXX |      | XXXXXXX | + (+ ) |      |           |      |      | XXX |      |       | ()(()(+)   | +###  |

| + + 4067                        |            | 9        | BC5      | 58E0    | D6D9  | 9 A+    | 7+ 5       | 6A2       | E7                | 4E   | 0C91    | 577( | 2B      | 23     | XX   | 4FD4      | 68   | 85C  | 497 | 2    | 91+   | + F0       | 056 D |

|                                 |            |          |          |         |       |         |            |           |                   |      |         |      |         |        |      |           |      |      |     |      |       |            |       |

|                                 |            |          |          |         |       |         |            |           |                   |      |         |      |         |        |      |           |      |      |     |      |       |            |       |

|                                 |            |          |          |         |       |         |            |           |                   |      |         |      |         |        |      |           |      |      |     |      |       |            |       |

|                                 |            |          |          |         |       |         |            |           |                   |      |         |      |         | 1      |      |           |      |      |     |      |       |            |       |

| 000                             | 00+ 0000   | )   +    | ( + )( + | • N + N | +   + | +    -  | + 00       | 900 +     | • XI+XI           | +    | NI+ N   | +    | AI IAI  | 00+    | NI I | NI IN     |      | IINI | MI  | INI  |       | 00-        | + 101 |

|                                 |            |          |          |         |       |         |            |           |                   |      |         |      |         |        |      |           |      |      |     |      |       | ורחרח ו    |       |

|                                 |            |          |          |         |       |         |            |           |                   |      |         |      |         |        |      |           |      |      |     |      |       |            |       |

|                                 |            |          |          |         |       |         |            |           |                   |      |         |      |         |        |      |           |      |      |     |      |       |            |       |

|                                 |            |          |          |         |       |         |            |           |                   |      |         |      |         |        |      |           |      |      |     |      |       |            |       |

|                                 |            |          |          |         |       |         |            |           |                   |      |         |      |         |        |      |           |      |      |     |      |       |            |       |

| 0000                            |            |          |          |         | 00    |         |            |           |                   |      |         |      |         | 0000   |      |           | 00   | 0000 |     |      |       |            |       |

|                                 |            |          |          | AEF 17  |       |         | au -       |           | 000 <b>0</b> 93AE |      |         |      |         |        | - W  | 000<br>B8 |      |      |     | 100/ |       | 000<br>000 |       |

|                                 |            | 9B4      |          |         |       |         | au -       |           |                   |      |         |      |         |        | - W  |           |      |      |     | 100/ |       | 1007       |       |

| 00+1990                         |            | <u> </u> | 1A 3.    |         | /534  | 3921    | 76         | 38        | 93AE              | B EA | 498     | 02D8 | 3283    |        | F9   | B8        | 9EC/ | A 8  | DØD | 62   | 218   | 1007       | c     |

| 00+ 1990<br>000                 |            |          | 1A 3.    | AEF 7   | /534  | 3921    | 76:<br>001 | 38        | 93AE              | B EA | 498     | 02D8 | 3283    |        | F9   | B8        | 9EC/ | A 8  | DØD | 62   | 218   | FØF        | c     |

| 00+ 1990<br>000                 |            |          | 1A 3.    | AEF 7   | /534  | 3921    | 76:<br>001 | 38<br>000 | 93AE              | B EA | 498     | 02D8 | 3283    |        | F9   | B8        | 9EC/ | A 8  | DØD | 62   | 218   | FØF        | c     |

| 00+ 1990<br>000                 |            |          | 1A 3.    | AEF 7   | /534  | 3921    | 76:<br>001 | 38<br>000 | 93AE              | B EA | 498     | 02D8 | 3283    |        | F9   | B8        | 9EC/ | A 8  | DØD | 62   | 218   | FØF        |       |

| 0000<br>00+ 1990<br>000<br>Idle |            |          | 1A 3.    | AEF 7   | /534  | 3921    | 76:<br>001 | 38<br>000 | 93AE              | B EA | 498     | 02D8 | 3283    |        | F9   | B8        | 9EC/ | A 8  | DØD | 62   | 218   | FØF        | c     |

## e logic and non-synchronous designs and a FIFO

### **DEEPENING THE TESTING STACK**

|   | Test Type           | Example                |

|---|---------------------|------------------------|

| _ | Bench               | Hardware               |

|   | HW Integration      | Hardware in the loop   |

|   | Timing Verification | Timing Analysis        |

|   | Simulation          | Test bench             |

|   | Unit Test           | Functional             |

|   | HDL Compilation     | Latch detection        |

| _ | HDL Generation      | Write-before read, etc |

|   | Rust Compilation    | Type correctness       |

|   | Rust Linting        | Unused expressions     |

|   | Language Server     | Editor squiggles       |

```

#[test]

► Run Test | Debug

fn test_opalkelly_xem_6010_synth_ddr_stress() {

let mut uut: OpalKellyDownloadDDRFIF0StressTest = OpalKelly

uut.hi.link_connect_dest();

uut.mcb.link_connect_dest();

uut.raw_sys_clock.connect();

uut.connect_all();

xem6010::synth::synth_obj(uut, dir: target_path!("xem_6010/

ddr::test_opalkelly_ddr_stress_runtime(

bit_file: target_path!("xem_6010/ddr_stress/top.bit"),

serial_number: env!("XEM6010_SERIAL"),

) Result<(), 0kError>

unwrap()

```

### **CRATES.IO AND THE SHARE ECOSYSTEM**

- Board support packages (BSPs) provide hardware and FPGA specific support

- Easily shared on crates.io.

- Anyone can package up and contribute

- Meta-programming features

- ► BSPs

- Reusable circuit components

- Rust & cargo provide excellent version management

- Semantic versioning for hardware

### crates.io/search?q=rust-hdl

**rust-hdl** v0.46.0

Write firmware for FPGAs in Rust

Homepage Repository

### wrap\_verilog\_in\_rust\_hdl\_macro v0.1.1

A proc-macro to wrap Verilog code in a rust-hdl module

Homepage Repository

### extract\_rust\_hdl\_interface v0.2.0

Extracts the information needed for a rust-hdl module from a verilog module

Homepage Repository

rust\_hls\_macro v0.2.0

High level synthesis support for rust-hdl

Homepage Repository

### rust-hdl-bsp-step-mxo2-lpc v0.1.2

rust-hdl board support package for STEP-MXO2-LPC

# **EARLY USER FEEDBACK**

- Need more language features to make it feel more "Rusty":

- Local variables

- Type inference

- Match/if expressions

- Early returns

- Want rich enums, structs, arrays, etc

- Fewer foot guns, more backends, etc.

```

fn update() {

// v--- local variable with inferred type

let a = match self.state {

// ^--- match expression

State::Idle => return(3);

// Early returns ---^

State::Busy => 1,

};

```

```

enum OpCode {

Noop,

Jump(b24),

Load{dest: Register, src: Register},

Save([b56; 8])

```

### CLOCKING FOOT GUN

- With multiple clock domains, Clock type is not enough

- Which clock?

- Which signals go with what clock?

- RustHDL is no help here...

- Ideally, the type system should constrain:

- Signal type

- Signal direction

- Signal time domain

| 13 | <pre>#[derive(LogicBlock, Default)] 3 implementations</pre>                                |

|----|--------------------------------------------------------------------------------------------|

| 14 | <pre>pub struct AsynchronousFIF0<d: const="" n:="" pre="" synth,="" usize,<=""></d:></pre> |

| 15 | <pre>// Read interface</pre>                                                               |

| 16 | pub read: Signal <in, bit="">,</in,>                                                       |

| 17 | <pre>pub data_out: Signal<out, d="">,</out,></pre>                                         |

| 18 | <pre>pub empty: Signal<out, bit="">,</out,></pre>                                          |

| 19 | <pre>pub almost_empty: Signal<out, bit="">,</out,></pre>                                   |

| 20 | <pre>pub underflow: Signal<out, bit="">,</out,></pre>                                      |

| 21 | pub read_clock: Signal <in, clock="">,</in,>                                               |

| 22 | pub read_fill: Signal <out, bits<np1="">&gt;,</out,>                                       |

| 23 | // Write interface                                                                         |

| 24 | <pre>pub write: Signal<in, bit="">,</in,></pre>                                            |

| 25 | <pre>pub data_in: Signal<in, d="">,</in,></pre>                                            |

| 26 | <pre>pub full: Signal<out, bit="">,</out,></pre>                                           |

| 27 | <pre>pub almost_full: Signal<out, bit="">,</out,></pre>                                    |

| 28 | <pre>pub overflow: Signal<out, bit="">,</out,></pre>                                       |

| 29 | <pre>pub write_clock: Signal<in, clock="">,</in,></pre>                                    |

| 30 | <pre>pub write_fill: Signal<out, bits<np1="">&gt;,</out,></pre>                            |

| 31 | // Internal RAM                                                                            |

| 32 | ram: RAM <d, n="">,</d,>                                                                   |

| 33 | // Read Logic                                                                              |

| 34 | <pre>read_logic: FIFOReadLogic<d, block_size="" n,="" np1,="">,</d,></pre>                 |

| 35 | // write logic                                                                             |

| 36 | <pre>write_logic: FIFOWriteLogic<d, block_size<="" n,="" np1,="" pre=""></d,></pre>        |

|    |                                                                                            |

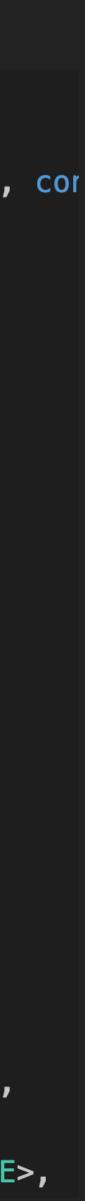

# RHDL

- Build a complete co-compiler

- Provide type inference, etc.

- Far more Rust-like

- Fewer surprises and limitations

- Easier to use, harder to build

- Stay tuned...

# RHDL throughout the years.

- Samit Basu

- basu.samit@gmail.com

- Special thanks to the folks that have supported RustHDL and

- Especially J. Vernet, T. Witzel, and the Digital Forge team.

- Also special thanks to TheZoq2 for encouraging me to talk about it!